pascal писав:може хтось пояснить?

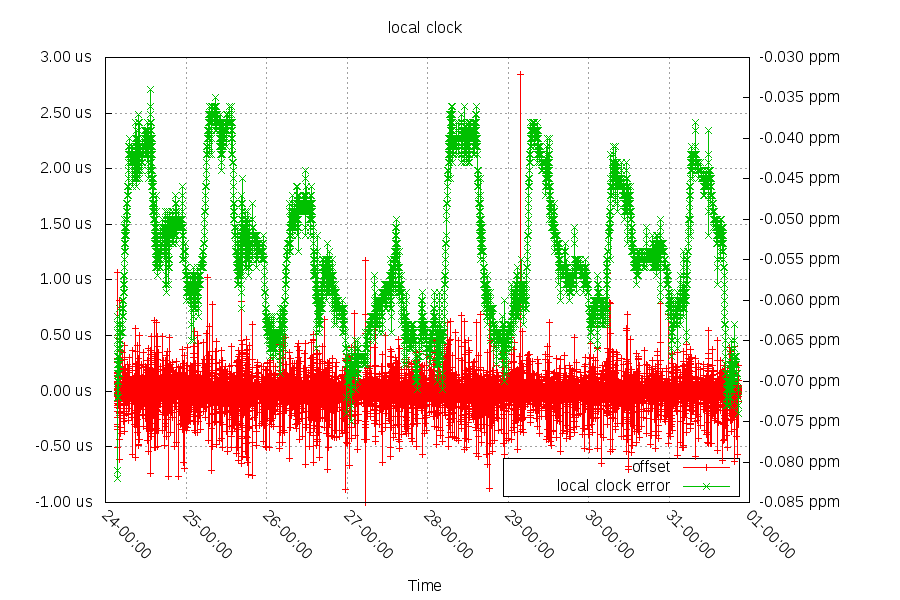

в компютері в якості clocksource для realtime ядра використовується системний clock (HPET) у якого частота 10MHz що дає затримки порядку 100 наносекунд або TSC clock з затримкою близько 4 наносекунди. ще включається PCI интерфейс з своїм APIC clock джерелом

а в ARM платформах як реалізовується внутрішня синхронізація програмних компонентів? які параметри в

/sys/devices/system/clocksource/clocksource0/current_clocksource

512 samples/44.1 kHz = 11.7 ms я так розумію що затримки повинні бути меншими чим 1 семпл, щоб забеспечити вчасний фронт сигналу.

на виских рівнях роздільчої здатності воні мають бути відповідно ще меншими.

А шо, не можна подивитися які клоки доступні в

/sys/devices/system/clocksource/clocksource0/available_clocksource

тай попробувати? Їх же можна міняти, правда ж?